File Name: cadence smv manual.pdf Size: 4779 KB Type: PDF, ePub, eBook Category: Book Uploaded: 18 May 2019, 22:26 PM Rating: 4.6/5 from 742 votes.

### Status: AVAILABLE

Last checked: 10 Minutes ago!

In order to read or download cadence smv manual ebook, you need to create a FREE account.

**Download Now!**

eBook includes PDF, ePub and Kindle version

- **<u>Register a free 1 month Trial Account.</u>**

- **Download as many books as you like (Personal use)**

- **Cancel the membership at any time if not satisfied.**

- **Join Over 80000 Happy Readers**

#### **Book Descriptions:**

We have made it easy for you to find a PDF Ebooks without any digging. And by having access to our ebooks online or by storing it on your computer, you have convenient answers with cadence smv manual . To get started finding cadence smv manual , you are right to find our website which has a comprehensive collection of manuals listed.

Our library is the biggest of these that have literally hundreds of thousands of different products represented.

×

# cadence smv manual

I will use the mailing listThe GUI version is called vw Note that you need to run these onEveryone is expected toThese studentsPoor questions will countAssignments will not be accepted beyond the due date without priorDesign covers theF for the course, in accordance with WPIsYour only chance to avoid an NR or F is. SATABS requires a code preprocessing environment comprising of aStudio Express . You need to install a Model Checker in order to be ableAvailable from The free versionThe documentation for SMV can be found in the directory where You must addSATABS uses Cadence SMV by default. InstallationThe directory containing the NuSMV binary should be addedUse the option BOPPO relies on a builtin SAT solver and Quantor, a solverUse the option The binaries are available from Try running SATABS. These methods allow the verification of Cadence SMV provides a variety of such techniques We use the data type ordset to model the round numbers of the protocol, which are unbounded,Furthermore, the scheme is modelled by requiring that the value of theThus, counting votes, i.e. expressing conditions of the form. To overcome this, instead of modelling a party reading individual votes,The protocol is not affected as the votes remain unchanged once they have been made. Furthermore, we consider the totals of the honest parties and the corrupted parties

separately.http://www.nexiagroup.com.ar/prod\_images/dewalt-xrp-drill-manual.xml

• 1.0.

The main reason for this, although it also allows us to simplify the model, is to dealIn fact, since we have proved that see the properties corrupted5 and corrupted6 in the additional invariants section Observe that, since once these votes have been readTherefore, casting prevotes at this earlier point Note that, since the coin for round r might not be revealed when a prevote is now cast, The motivation behind this change is that the proof of Furthermore, since the preprocessing votes require no justification, it follows that the adversary has the power toWe us this fact, and hence do not store the preprocessing votes of the corrupted parties. The remaining assumptions concern fairness statements which ensure that parties eventually cast votes, In particular, since variables of different ordset These properties follow from the fact if this was not true there would be at leastNow, if this party does not decide in round r, If a party decides in round r, then by Agreement. On the other hand, if no party decides before round r, Therefore we assume that The proofs of P5 P6 can be found in the additional invariants section First we require the following lemma.Now since all parties Then since all parties The following proposition is crucial to establishing the efficiency of the protocol.We prove the proposition by induction on r. For any state s reached just before the coin is tossed. These methods allow the verification of Cadence SMV provides a variety of such techniques We achieve this by suitably combining data type reduction ordset with Note that the version of Cadence SMV we have used is not fully compatible with the release of 08.08.00.To simplify the proof and to keep the model checking feasibleThe complete proof of Invariant 6.3. Citations 7 References 16 Abstract Embedded systems are becoming increasingly popular due to theirFor safetycritical applications an approach is In this paper we Cadence

SMV.http://www.dialogosconsultoria.com.br/userfiles/dewalt-xrp-hammer-drill-manual.xml

We constructed a Verilog model of the system by integratingReguest fulltext Advertisement Citations 7 References 16. Authors in Kherbouche et al., 2012, use a kind of transition system with a few specific characteristics called Kripke Structure. Despite that FSM has lack of expressiveness and the state explosion problem might be a limitation from practical representation of complex control behavior, Kripke structure has a strong point is that its an input semantic language of several model checkers like Mcheck Sember, 2005, MlSolver Oliver and Martin, 2008, Xspin Ruys, 1999, UPPAAL, Cadence Mir et al., 2000, etc and more precisely NuSMV. In addition to that it can be tested with a temporal logic requirements.. A New Approach for the Verification of BPMN Models Using Refinement Patterns Conference Paper Fulltext available Jul 2018 Salma Ayari Bendaly Hlaoui Yousra Leila Ben Ayed View. As existing functional testing methods fall short in detecting these unspecified often malicious logic, formal methods provide powerful solutions in detecting malicious behaviors in hardware. Toward this direction, we will discuss theorem proving and model checking for hardware trust evaluation. Specifically, proofcarrying hardware PCH and its applications are introduced in detail. While PCH methods suffer from scalability issues and cannot be easily used for largescale applications such as SystemonChip SoC design, we will also discuss variants of PCH such as the Hierarchy Preserving Formal Verification framework, for alleviating the scalability challenge. View Show abstract. Discovering nondeterminism manually is infeasible for industrialsized systems. Solutions in the literature lack the capability to analyze infinitestate systems. We leverage the nuXmv model checker to analyze unbounded domains and implement an algorithm that systematically computes a minimal set of comparable transitions for the SUD yet eliminates false positives by model checking.

To validate our approach, we analyze a realworld system and report discovered cases of nondeterminism. We employ Umples capability to convert state machines to nuXmv. View Show abstract. Other approaches are modelbased approaches. The verification process is performed at the RTL level of implementation, which has the advantage of being synthesizable by a synthesis tool. Cadence SMV is used as the verification tool. It employs the symbolic model checking technique. A stepwise verification method is proposed where the details of design are increased in each step. This method facilitates the error finding process. The proposed technique can reduce the complexity of the verification process and enables it to be completed in a reasonable time. The technique is illustrated on a simple processor used in an embedded Web server. The design is verified successfully. View Show abstract. Early development of such tools finds origins in automatatheoretic formal methods.From control engineering, thisFrom computer science, the research has incorporated the theories ofThe case study of an automated highway system is used to illustrate theThere is an equalUSA, 1998. Modeling and Veri cation of the Fairisle ATM Switch Fabric using MDGs Article Seghier Tahar Xian Song E. Cerny Otmane Ait Mohamed View MDG Model Checker Users Manual Article Y. Xu View An introduction to formal hardware verification Article C. Seger Formal hardware veri cation has recently attracted considerable interest. In addition, as the complexity of the designs increase, an ever smaller percentage of the possible behaviors of the designs will be simulated. Hence, the con dence in the designs obtained by simulation is rapidly diminishing. This paper provides an introduction to the topic by describing three of the main approaches to formal hardware veri cation theoremproving, model checking, and symbolic simulation.

### http://eco-region31.ru/3m-overhead-projector-9050-manual

We outline the underlying theory behind each approach, we illustrate the approaches by applying them to simple examples, and we discuss their strengths and weaknesses. We conclude the paper by describing current ongoing work on combining the approaches to achieve multilevel veri cation approaches. View Show abstract A Computational Logic Handbook Article Jan 1988 Robert S. Boyer Jstrother Moore View Formal Verification in a Commercial Settings Article Jan 1997 Robert P. Kurshan This tutorial addresses the following questions. View Show abstract Symbolic Model Checking An Approach to the State Explosion Problem Thesis Jan 1992 Kenneth L. McMillan View Multiway Decision Graphs for Automated Hardware Verification Article Feb 1997 FORM METHOD SYST DES Francisco Corella Zhongxiang Zhou Xian Song E. Cerny Traditional ROBDDbased methods of automated verification suffer from the drawback that they require a binary representation of the circuit. To overcome this limitation we propose a broader class of decision graphs, called Multiway Decision Graphs MDGs, of which ROBDDs are a special case. With MDGs, a data value is represented by a single variable of abstract type, rather than by 32 or 64 boolean variables, and a data operation is represented by an uninterpreted function symbol. MDGs are thus much more compact than ROBDDs, and this greatly increases the range of circuits that can be verified. We give algorithms for MDG manipulation, and for implicit state enumeration using MDGs. We have implemented an MDG package and provide experimental results. View Show abstract Automatic Datapath Abstraction In Hardware Systems. Conference Paper Jul 1995 Ramin Hojati Robert K. Brayton The biggest stumbling block to make formal verification widely acceptable is the state space explosion problem. Abstraction is used to simplify a design so that the number of reachable states is reduced.

https://duluthtaxiservice.com/images/brewstation-10-cup-dispensing-coffeemaker-47380-manual.pdf

ICS uses finite relations, interpreted and uninterpreted integer functions and predicates, interpreted memory functions, and supports nondeterminism and fairness constraints. As a subset, it includes finitestate systems with general fairness constraints. Verification in this framework is performed using language containment as follows. A linear time algorithm for recognizing these subsets is given. These results also hold for the standard finitestate systems and thus also provide some generic methods for automatic data abstraction for such systems. Using these results, we are able to verify a memory model by reducing integer data values to binary, and unbounded memory addresses to a small number. In some cases, the set of reachable states is finite, and the verification can be completed exactly. In other cases, given n, the verifier checks that no errors of length less than n exist. View Show abstract Symbolic Model Checking. Conference Paper Jan 1996 International Conference on Computer Aided Verification Edmund M. Clarke Kenneth L. McMillan Sergio Campos Vassili HartonasGarmhausen View Modeling and formal verification of the Fairisle ATM switch fabric using MDGs Article Fulltext available Jul 1999 IEEE T COMPUT AID D Sofiene Tahar Xian Song E. Cerny Otmane Ait Mohamed In this paper, we present several techniques for modeling and formal verification of the Fairisle asynchronous transfer mode ATM switch fabric using multiway decision graphs MDGs. MDGs represent a new class of decision graphs which subsumes Bryants reduced ordered binary decision di agrams ROBDDs while accommodating abstract sorts and uninterpreted function symbols. The ATM device we investigated is in use for real applications in the Cambridge University Fairisle network. We modeled and verified the switch fabric at three levels of abstraction behavior, and register transfer level RTL and gate levels.

http://dumaxsrl.com/images/brewmaster-hamilton-beach-manual.pdf

In a first stage, we validated the highlevel specification by checking specific safety properties that reflect the behavior of the fabric in its real operating environment. Using the intermediate abstract RTL model, we hierarchically com pleted the verification of the original gatelevel implementation of

the switch fabric against the behavioral specification. Since MDGs avoid model explosion induced by data values, this work demonstrates the effectiveness of MDGbased verification as an extension of ROBDDbased approaches. All the verifications were carried out automatically in a reasonable amount of CPU time.Inconsistencies in the assembly codeA formal model for an actual commercial microprocessor is established. This is done by modeling the instruction set and processor architecture. Embedded software takes the form of the assembly program code to be run on the processor. Specifications are given as CTL temporal logic formulae. The method has been implemented in the SMV model checker and is illustrated by a practical embedded system application a mouse controller. A typical SoC contains one or more microcontrollers, several peripherals and embedded memories. In the software arena, there is a whole lot of embedded software that goes into products, built using these complex SoCs. This creates a need for having a robust product flow, which enables different teams to work simultaneously and coherently. Traditionally, many of these development activities have always been mostly sequential in nature. This type of sequential flow cannot help in meeting the timetomarket requirements of todays consumer products. Some of the most popular alternatives to this kind of sequential development flow include a FPGA prototyping of the system b Develop prototype using Instruction Set Simulators ISS c Virtual System Prototyping VSP. The first option lacks the required flexibility and need to have the complete microarchitecture defined before designing the prototype.

Traditional ISS solutions are used for simulating processors with few or no peripVSP definitely addresses these issues. The concept of VSP is based on creating a software model of the entire hardware system including external components e.g. base station model for checking the base band systems. This model can be used to explore and analyze different architectures. Once an optimal architecture has been chosen, the same model can be used as an executable specification. SW teams can use VSP to start their development work, as soon as the architecture is defined and the corresponding VSP is available. As a part of this work, attempt has been made to highlight advantages and challenges of virtual prototyping with a case study. Read more Conference Paper Fulltext available Symbolic RTL simulation February 2001 A. Kolbi James Kukula Robert Damiano Symbolic simulation is a promising formal verification technique combining the flexibility of conventional simulation with powerful symbolic methods. Unfortunately, existing symbolic simulators are restricted to gate level simulation or handle just a synthesizable subset of an HDL. We present an approach that enables symbolic simulation of the complete set of RTlevel Verilog constructs with full delay support. Additionally, we propose a flexible scheme for introducing symbolic variables and demonstrate how error traces can be simulated with this new scheme. Finally, we present some experimental results on an 8051 microcontroller design which prove the effectiveness of our approach. View fulltext Conference Paper Fulltext available A balanced approach to highlevel verification performance tradeoffs in verifying largescale mult. February 2000 Dennis Abts M. Roberts David J. Lilja A single node of a modern scalable multiprocessor consists ofThis level ofIn this paper we examine theWe also provide a graphical representation of the reduced model, suitable for debugging and verification purposes.

## http://gennarimaq.com.br/wp-content/plugins/formcraft/file-upload/server/content/files/1626f50c0c2 bb4---bosch-wfd-1660-user-manual.pdf

We use the Cadence FormalCheck tool to verify designs properties on the abstracted reduced bus model translated into Verilog code. While the verification of the original model was not possible to perform, we succeeded in checking all properties on the reduced model. Read more Conference Paper On the design and verification methodology of the lookaside interface January 2005 Otmane Ait Mohamed S. Tahar Ansar Habibi Asif Iqbal Ahmed In this paper, we present a technique to design and verify the lookaside LA1 interface standard used in network processors. Our design flow includes several refinements starting from an informal UML specification until getting to an RTL

modeled in Verilog. The first one serves the verification by model checking of a set of PSL properties, while the second includes a set of assertions to be verified by simulation. To evaluate the performance of our approach, we used the rulebase model checker to verify the same properties; and the OVL library to verify the same assertions. The new capabilities of SystemC 2.0, such as those added for transactionbased communication and testbench Specification and monitoring, facilitate this SoC modeling. We describe such a methodology based on the SystemC Verification Standard implemented by Cadences TestBuilderSC. This methodology enables comparison of highlevel transaction level SoC models in SystemC against implementation RTL models. An application of the methodology is presented, based on the AMBA Class Library ACL for SystemC being developed by ARM in collaboration with EDA partners. The key elements of the methodology are 1. A completely reusable testbench that can be used for simulation and verification of the design at both highlevel transaction level of abstraction and RTL implementation level. 2. A single database format is used so that data collected from simulations at each level can easily be processed and compared.

We present an example of effective validation of ARM PrimeXsysplatform IP components against their RTL implementation. Read more Article Integrating Formal, Soft and Diagrammatic Approaches in HighLevel Synthesis and HardwareSoftware C. June 2002 Andras Orban Zoltan Adam Mann In this paper, preliminary results and research directions in highlevel synthesis and hardwaresoftware codesign are presented. The main methods are demonstrated on two case studies. The first one shows the usage of formal and soft methods application of graph theory, constraint logic programming and a genetic algorithm on the scheduling problem of highlevel synthesis. Both case studies show methods that are usually employed in hardware design only, but their usage in software design would also be possible. At the end of the paper, a hardwaresoftware codesign framework is suggested that integrates all these approaches with the designerfriendly diagrammatic techniques of software design. Read more Conference Paper Environment synthesis for compositional model checking February 2002 Hong Peng Yassine Mokhtari Sofi Ene Tahar Modeling the environment of a design module under verification is a known practical problem in compositional verification. In this paper, we propose an approach to translate an ACTL specification into such an environment. Throughout the translation, we construct an efficient tableau for the full range of ACTL and synthesize the tableau into Verilog HDL behavior level program. We have used the proposed environment synthesis in the compositional verification of an ATM switch fabric from Nortel Networks. Experiments show that given the theoretical compositional verification intractable limit, we can still manage to verify industry size designs.

Read more Article A hierarchical approach to the formal verification of embedded systems using MDGs January 1999 Subhashini Balakrishnan Embedded systems are finding widespread application including communication systems, factory automation, graphics and imaging systems, medical equipment and even household appliances. The approach is demonstrated on the embedded software for a mouse controller application on a commercial microcontroller PIC 16C71 from Microchip Technologies Inc. The embedded system is modeled at different levels of the design hierarchy i.e., the microcontroller RT level, the microcontroller Instruction Set Architecture ISA, the embedded software assembly code level and the embedded software flowchart specification. The correctness of the system hardware platform in implementing its intended architecture is established by formally verifying the equivalence between the RTL hardware and the ISA, using the MDG sequential equivalence checking tool. The next step is taken to verify the particular application embedded in the system by checking the equivalence between the assembly code and its intended behavior, specified as a flowchart. Further verification is done on the models through the property checking procedure provided by the MDG tools. Liveness properties are also checked using the newly developed MDG model checking procedure. Inconsistencies in the assembly code with respect to the specification, as published in the application notes of the manufacturer, were uncovered

through the verification experiments. The design under investigation is a telecom system block, which processes a portion of the synchronous optical network SONET line overhead of a received data stream. We adopted a hierarchical modelling and verification approach which follows the natural design hierarchy. The verification has been performed using both equivalence and model checking.

To measure the performance of the MDGbased model checking, we also conducted a comparative verification of the same design using Cadence FormalCheck. The design considered is a commercial product obtained from PMCSierra, Inc.One design error which could lead the system into a hangup state was detected through the verification of a set of liveness and safety properties. The design error was also confirmed through SynopsysVSS and VerilogXL simulations. Read more Conference Paper A system for synthesizing abstractionenabled simulators for binary code verification August 2010 Dominique Guckel Jorg Brauer Stefan Kowalewski Formal verification of embedded software is crucial in safetycritical applications, ideally requiring as little human intervention as possible. Binary code model checking based on hardware simulators already comes close to this goal, although with high initial effort for developing a simulator of the respective target platform. To remedy this drawback, we describe a system for automatically synthesizing simulators, which are suited for model checking in that they support automatic abstraction. We evaluate the practicality of this approach by synthesizing simulators for the Atmel ATmega16 and Intel MCS51 microcontrollers. Read more Discover more Last Updated 29 Mar 2020 Download citation What type of file do you want. RIS BibTeX Plain Text What do you want to download. Citation only Citation and abstract Download ResearchGate iOS App Get it from the App Store now. Install Keep up with your stats and more Access scientific knowledge from anywhere or Discover by subject area Recruit researchers Join for free Login Email Tip Most researchers use their institutional email address as their ResearchGate login Password Forgot password. Keep me logged in Log in or Continue with LinkedIn Continue with Google Welcome back. Keep me logged in Log in or Continue with LinkedIn Continue with Google No account. All rights reserved. Terms Privacy Copyright Imprint.

Conference Proceedings. Navigating to a New Era Cat. No.00TH8492 Embedded systems are becoming increasingly popular due to their widespread applications. For safetycritical applications an approach is needed to validate the complexity of VLSI designs at a higher abstraction level. With formal verification we verify that every possible behavior of the target system satisfies the specification. SHOWING 14 OF 4 REFERENCES Multiway Decision Graphs for Automated Hardware Verification F. Corella, Z. Zhou, X. Song, M. Langevin, E. Cerny Computer Science Formal Methods Syst. Des. 1997 An Introduction to Formal Verification, Technical Report 9213 UBC, Department of Computer Science, 1992 Getting Started with SMV; User's Manual Cadence Berkeley Laboratories, 1998 Symbolic model checking K. McMillan Computer Science 1993 Related Papers Abstract Figures, Tables, and Topics 12 Citations 4 References Related Papers The Allen Institute for AI Proudly built by AI2 with the help of our Collaborators using these Sources. All results we obtained in verification and simulation with NuSMV are presented in the paper. aei.tuke.sk Save to Library Create Alert Cite Launch Research Feed Share This Paper Figures and Topics from this paper. Thirteenth Annual IEEE Symposium on Logic in Computer Science Cat. No.98CB36226 1998 Logic in Computer Science Modelling and Reasoning About Systems V. Goranko Computer Science Journal of Logic, Language and Information 2007 Principles of Model Checking, Formal Methods and Tools Group, University of Twente 2004 VIEW 3 EXCERPTS HIGHLY INFLUENTIAL Acta Electrotechnica et Informatica Acta Electrotechnica et Informatica 2009 Cadence. Getting started with SMV Cadence. Source publication Integrating formal verification and highlevel processor pipeline synthesis Conference Paper Fulltext available Jul 2011 Eriko Nurvitadhi James C.

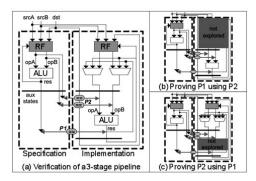

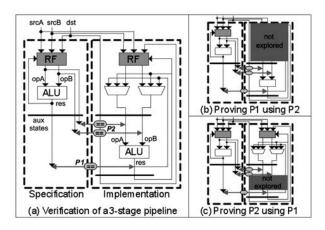

Hoe Timothy Kam ShihLien Lu When a processor implementation is synthesized from a specification using an automatic framework, this implementation still should be verified against its specification

to ensure the automatic framework introduced no error. This paper presents our effort in integrating fully automated formal verification with a highlevel processor pipeline synthes. Cite Download fulltext Contexts in source publication Context 1. Each ALU instruction reads two operands from the register file RF; performs an ALU operation; and writes the result back to the RF.. View in fulltext Context 2. ALU instruction reads two operands from the register file RF; performs an ALU operation; and writes the result back to the RF.Keep me logged in Log in or Continue with LinkedIn Continue with Google Welcome back. Keep me logged in Log in or Continue with LinkedIn Continue with Google No account. All rights reserved. Terms Privacy Copyright Imprint. The alternative dates for the exercise will be on June 15 2005 and June 22 2005. The next exercise will take place on 25.05.2005. Other lecture dates will be held as planned. SMV was developed by Ken McMillan. There are different versions of SMV. The first version is CMU SMV. CMU SMV does CTL model checking. The newer version is Cadence SMV. Cadence SMV supports CTL and LTL Model Checking, but concentrates on LTL model checking. Besides these originals there are some reimplementations and modified SMV versions. We will be using Cadence SMV in the exercise. SPIN was developed by Bell Labs and is available for free since 1991. SPIN is a LTL model checker that concentrates on software verification. There are a bunch of modified versions RTSPIN, dSPIN, etc. We will be using the original for the exercise. It was developed in cooperation with the university of Aalborg and the Uppsala university. Uppaal concentrates on the verification of safetyconditions. The specification of attributes is carried out through a subset of CTL.

Downloads bib Abstract. The algorithm guarantees termination in the presence of stopping failures within polynomial expected time. Processes proceed through possibly unboundedly many rounds; at each round, they read the status of all other processes and attempt to agree. Each attempt involves a distributed random walk when processes disagree, a shared coinipping protocol is used to decide their next preferred value. Achieving polynomial expected time depends on the probability that all processes draw the same value being above an appropriate bound. For the nonprobabilistic part of the algorithm, we use the proof assistant Cadence SMV to prove validity and agreement for all N and for all rounds. The coinipping protocol is verified using the probabilistic model checker PRISM. For a finite number of processes up to 10 we automatically calculate the minimum probability of the processes drawing the same value. The correctness of the full protocol follows from the separately proved properties. This is the first time a complex randomized distributed algorithm has been mechanically verified.

http://www.bosport.be/newsletter/3m-overhead-projector-9050-manual